Sensicomm LLC - DSP design services.

Algorithms, software and hardware for sensors, signal processing, and communications.Home About Contact Publications Projects Downloads Sitemap Blog

I've also used the Atmel AVR family of microcontrollers in some projects. They are nice chips - economical, flexible, and easy to program. So, I've been experimenting with the AX8 core from opencores.org as a way to leverage my AVR-based tools and code.

![]() I am posting tips and examples here that I think may be useful

to others. Keep in mind, however, that this is partly a learning

experience for me, so don't expect them to be bug-free. They

haven't killed my cat (or my FPGA), but I can't guarantee that they

won't kill yours.

I am posting tips and examples here that I think may be useful

to others. Keep in mind, however, that this is partly a learning

experience for me, so don't expect them to be bug-free. They

haven't killed my cat (or my FPGA), but I can't guarantee that they

won't kill yours.

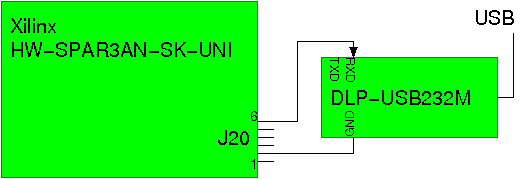

The AX8 package on opencores includes a simulation of the

key components of an AT90S2313 chip, including I/O ports,

timers, and UART. I wrote a test program to send a fixed

pattern to the UART, and built the VHDL modules. It's working.

The AX8 package on opencores includes a simulation of the

key components of an AT90S2313 chip, including I/O ports,

timers, and UART. I wrote a test program to send a fixed

pattern to the UART, and built the VHDL modules. It's working.

data2mem that allows you to update just the

program in an on-chip RAM without running the full build process.

Only problem is that it's a really complicated program with a lot of options,

so it took a while to get things working.

The best starting point I found is the tutorial by Arnim Läuger at home.mnet-online.de/al/BRAM_Bitstreams.html. I ended up with something similar, but made a few changes to adapt to differences in the core that I'm using.

process (A_r)

begin

case to_integer(unsigned(A_r)) is

when 000000 => D <= "1110111110001111"; -- 0x0000

when 000001 => D <= "1011101110000001"; -- 0x0002

ADDRESS_MAP avrmap PPC405 0

ADDRESS_SPACE rom_code RAMB16 [0x00000000:0x000007FF]

BUS_BLOCK

avrchip/rom/RAMB16BWE_S18_S9_inst [15:0];

END_BUS_BLOCK;

END_ADDRESS_SPACE;

END_ADDRESS_MAP;

avrchip/rom/... string needs to be right, or the program won't

work. Here's how I built it:

jr_formisc.vhd defines a top-level entity

that connects to the I/O pins of the FPGA. It

instantiates the entity A90Smisc

with the name avrchip

architecture rtl of jr_formisc is

...

avrchip : A90Smisc port map (

A90Smisc.vhd, there's an instantiation of

entity mem_1kx16 named rom.

entity A90Smisc is

...

architecture rtl of A90Smisc is

...

rom : mem_1kx16 port map(

mem1.vhd, there's an instantiation

of the RAM block. This definition is based on the Xilinx-supplied

templates (in ISE, Edit > Language Templates, then

drill down to Block RAM and

then Dual Port (Mis-matched Port Width).

RAMB16BWE_S18_S9_inst : RAMB16BWE_S18_S9

generic map (

# grep RAMB16BWE_S18_S9_inst *.mrp

block:<avrchip/rom/RAMB16BWE_S18_S9_inst>:<RAMB16BWE_RAMB16BWE>.

pgm.hex in Intel hex format,

srec_cat ../t03_pgm/pgm.hex -Intel -Byte_Swap 2 -o pgm.mem -vmem 8

Generate Programming File step. This creates

2 files

Now we can update the bit file

data2mem -bm jr_try1_bd.bmm -bt jr_formisc.bit -bd pgm.mem -o b modified.bit

jr_formisc.bit has the original

AX8 program that's defined in mem1.vhd, and modified.bit

has the new program.

You chan check the changes with

data2mem -bm jr_try1_bd.bmm -bt jr_formisc.bit -d > old.txt

data2mem -bm jr_try1_bd.bmm -bt modified.bit -d > new.txt

diff old.txt new.txt

Source is now available under the GPL. See

ax8_experiment1 on the

download page.(Feb 6,2009: downloads

are temporarily down. Check back in a few days.)